# Designing the Sine Wave Quiet Converter

Colonel W. T. McLyman Kg Magnetics, Inc. P.O. Box 3703 Idyllwild, CA 92549-3703

Abstract- A few designers have known about the Resonant Converter described here for many years. This type of Resonant Converter has been built mainly in the range of 200 watts to 2 kilowatts, and has been used as a static inverter. However, it has remained relatively obscure in the general literature. The Quiet Converter was developed at Jet Propulsion Laboratory (JPL), Division 38, to power very sensitive instruments. The Quiet Converter produces a sinusoidal voltage across a parallel resonant tank. The inherent low noise from this converter is how the nickname, Quiet Converter, came about. Programs at Jet Propulsion Laboratory (JPL) that have successfully used the low noise environment of the Quiet Converter are, WF/PC-II, Articulated Fold, Mirror Actuators, (Hubbell Space Telescope), MISR (Earth Orbiting System), Raman, Mars 05 ONC and SIM's, CCD Cameras.

# Introduction

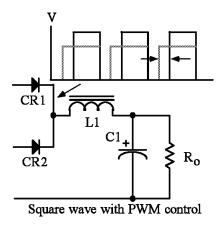

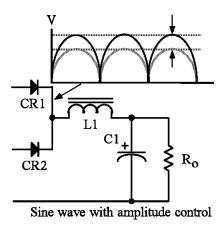

The Quiet Converter produces a sinusoidal voltage across a parallel resonant tank. The dc output voltage is obtained after rectification and filtering of the sinusoidal secondary voltage. The regulation is achieved by controlling the duty-cycle to the tuned tank by the switching transistors. A comparison of the standard type of PWM control is shown in Figure 1 and the Quiet Converter with its amplitude modulation (AM), shown in Figure 2. This paper will use cgs units.

Fig. 1. Standard Type PWM Control.

**Fig. 2.** Quiet Converter with its Amplitude Modulation.

## Comparing the Square and Sine wave Converter

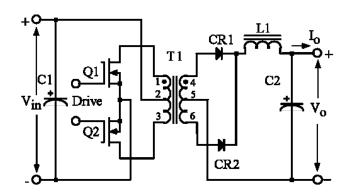

The voltage-fed square wave converter circuit is the most widely-used, converter topology. In a voltage-fed converter, the powder source,  $V_{in}$ , is connected directly to the transformer through a transistor, Q1, as shown in Figure 3. When the transistor, Q1, is switched on, the full source voltage is applied to the transformer, T1, primary, (1-2). The transistor saturation will be ignored. Conversely, when Q2 is switched on, the full source voltage is applied to the other half of the transformer, T1, primary, (2-3). The primary source voltage,  $V_{in}$ , is directly impressed onto the primary of the transformer, T1, and therefore, the voltage across the transformer, T1, is always a square wave.

Fig. 3. Typical Square Wave Type Converter.

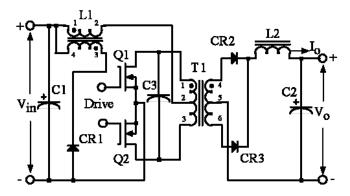

The main difference between a voltage-fed converter and a current-fed converter is the series inductor, L1 and the tank capacitor, C3, shown in Figure 4. The inductor, L1, is commonly called a feed-choke or series inductor. It has an inductance large enough in value to maintain a continuous current through the circuit under all conditions of line and load. Also, the series inductor, L1, isolates the input dc source from the sine wave voltage across the primary of the transformer, T1. The tank capacitor, C3, tunes the transformer, T1, to the natural operating frequency of the converter.

Fig. 4. Paralleled Tuned Sine Wave Converter.

#### **Series Inductor L1**

In order to incorporate pulse width modulation (PWM), or a drive circuit that has inherent dead time in which neither transistor is conducting, there must be a means to commutate the current in the series inductor, L1. Adding a winding to the series inductor, L1, is a simple way to commutate the current. When the current flowing in winding, (1-2), is interrupted, the current will now be commutated to the added winding, (3-4).

This procedure is done when connected with proper phasing, through a diode CR1, then, connected back to the dc source to complete the path, as shown in Figure 4. Now, when either transistors, Q1 or Q2, are interrupted, the added winding of the series inductor, L1, commutates the current back into the dc source, thus preventing the destruction of the switching transistors, Q1 and Q2.

## **Transformer Core Material, T1**

The Quiet converter, shown in Figure 4, has changed the operational performance dramatically compared to the square wave converter, shown in Figure 3. The transformer, T1, must have the correct inductance in order to operate correctly. Depending on the design environment the core material can be either a molypermalloy powder core, (MPP), or a ferrite core with a gap. The reason for using a powder core is because it has a built-in gap required for the tank circuit and these cores are available with temperature stabilized permeability. The use of a gap ferrite would perform just as well, but the design must be stable

over temperature. The tuning capacitor, C3, should be of high quality with a low ESR and should be stable. The capacitors that were used in the flight power supplies were plastic film, type CRH, to MIL-C-83421.

#### **Quiet Converter Waveforms**

The current-fed, sine wave converter waveforms are referenced from Figure 4. The waveforms presented here are copies drawn from an actual photo taken with an oscilloscope camera.

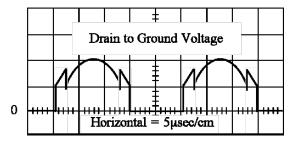

The drain voltage waveform of Q1 is shown in Figure 5. The notches in the waveform, seen in Figure 5, are caused by the dead time or dwell. The converter is properly tuned to the natural frequency.

Fig. 5. The Tuning Capacitor C3 is Correct.

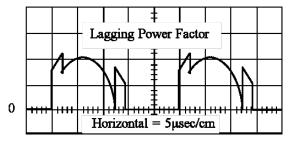

The drain voltage waveform of Q1 is shown in Figure 6. The converter is improperly tuned to the natural frequency. The resonant tank capacitor is too small in value.

Fig. 6. The Tuning Capacitor C3 is to Small.

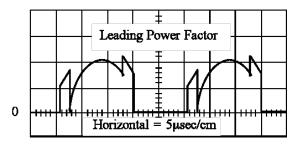

The drain voltage waveform of, Q1, is shown in Figure 7. The converter is improperly tuned to the natural frequency. The resonant tank capacitor is too large in value.

Fig. 7. The Tuning Capacitor C3 is to Large.

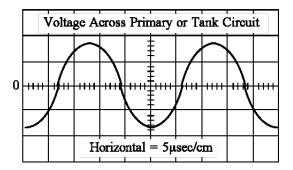

The primary voltage waveform is shown in Figure 8, across transformer, T1. The converter is properly tuned to the natural frequency.

Fig. 8. Voltage Waveform across Transformer, T1.

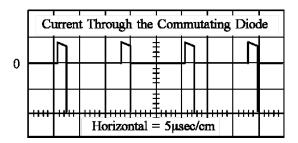

Commutating diode current waveform is shown in Figure 9. The current is through the series inductor, L1, winding (3-4). The converter is properly tuned to the natural frequency.

Fig. 9. Current Through the Commutating Diode.

### Maximum Transistor on Time, ton(max).

The maximum transistor on time,  $t_{on(max)}$ , is: Transistor drive circuits, such as a pulse width modulator (PWM) chip, will have a minimum of dead time,  $t_d$ . This dead time or dwell is shown in Figure 10.

$$t_{on(\max)} = \left(\frac{T}{2}\right) - t_d, \quad [\mu \text{sec}] \quad [1]$$

$$Q1 \qquad \qquad ton \qquad t$$

$$Q2 \qquad \qquad ton \qquad t$$

$$Q2 \qquad \qquad ton \qquad t$$

Fig. 10. Base Drive Voltage Dwell Time.

This dwell time, t<sub>d</sub>, will have a significant impact the applied ac voltage to transformer, T1. As seen in Figure 5 this dwell time can have a large effect on the applied voltage.

The conversion factor,  $K_a$  is:

$$K_{a} = \frac{\left(4t_{on(\text{max})} - T\right)}{TSin\left(\frac{t_{on(\text{max})}180}{T}\right)}, \quad [2]$$

# Calculating the Apparent Power, Pt

The apparent power,  $P_{t_i}$  is the power associated with the geometry of the transformer. The designer must be able to make allowances for the rms power in each winding. The primary winding handles,  $P_{in}$ , the secondaries handle,  $P_{o}$ , to the load. Since the power transformer has to be designed to accommodate the primary power,  $P_{in}$ , and the secondary,  $P_{o}$ , then by definition:

$$P_{t} = P_{in} + P_{\Sigma}, \text{ [watts]}$$

$$P_{\Sigma} = P_{o1} + P_{o2} + \dots P_{on}$$

$$P_{in} = \frac{P_{\Sigma}}{\eta}, \text{ [watts]}$$

$$P_{t} = \frac{P_{\Sigma}}{\eta} + P_{\Sigma}, \text{ [watts]}$$

$$\eta = \text{efficiency}$$

Because of the different winding configurations, the apparent power,  $P_t$ , of the transformer will have to be summed to reflect these differences. When the winding has a center tap and produces a discontinuous current, then the power in that winding, whether it is primary or secondary, has to be multiplied by the factor, U, to correct for the rms current in that winding. If the winding has a center tap, then, U = 1.41; if not, then, U = 1. Summing the output power of a multiple-output transformer would be:

$$P_{\Sigma} = P_{o1}(U) + P_{o2}(U) + \dots P_{on}(U), [4]$$

## **Design Equation Steps for the Quiet Converter**

1. The transformer secondary voltage,  $V_s$ , is:  $V_o = Output \ voltage$

$V_d = Diode Drop$

$$V_s = (V_o + V_d), \text{ [volts] [5]}$$

**2.** The maximum secondary true power,  $P_{s(max)}$ , is:

$$P_{s(\text{max})} = V_s \left( I_{o(\text{max})} \right)$$

[watts] [6]

**3.** The minimum secondary true power,  $P_{s(min)}$ , is:

$$P_{s(\min)} = V_s \left( I_{o(\min)} \right)$$

, [watts] [7]

**4.** The secondary apparent power,  $P_{sa}$ , is:

U = 1.41, center tapped winding

U = 1.0, single winding

$$P_{sa} = V_s \left(I_{o(\text{max})}\right)(U), \text{ [watts] [8]}$$

5. If, there is more than one output, then, sum the total secondary maximum apparent load power,  $P_{\text{sa}\Sigma}$ , maximum load power,  $P_{\text{ot}(\text{min})}$ .

$$P_{sa\Sigma} = P_{sa01} + P_{sa02} + ....,$$

[watts] [9]

$$P_{ot(\text{max})} = P_{o01(\text{max})} + P_{o02(\text{max})} + ....,$$

[watts] [10]

$$P_{ot(\min)} = P_{o01(\min)} + P_{o02(\min)} + \dots$$

, [watts] [11]

**6.** The maximum reflected secondary load resistance,  $R_{(max)}$ , is:

$R_{(max)}$  = Resistance Value

$\eta = Efficiency$

$$R_{\text{(max)}} = \frac{(V_{in})^2 (\eta)}{P_{ot(min)}}, \text{ [ohms] [ 12 ]}$$

7. The required series inductor inductance, L1, is: f = fundamental frequency

$$L1 = \frac{\left(R_{\text{(max)}}\right)}{3\omega}, \text{ [henrys] [ 13 ]}$$

**8.** The total period, T, is:

$$T = \frac{1}{f} (10^6)$$

, [ $\mu sec$ ] [ 14 ]

**9.** The maximum transistor on time,  $t_{on(max)}$ , is: (See Figure 10.)

$$t_{on(\text{max})} = \left(\frac{T}{2}\right) - t_d$$

, [ $\mu$ sec] [15]

10. The conversion ratio,  $K_a$ , is:

$$K_a = \frac{\left(4t_{on(\text{max})} - T\right)}{TSin\left(\frac{t_{on(\text{max})}180}{T}\right)}, [\text{ factor}] [16]$$

11. The peak voltage,  $V_{c(pk)}$ , on the resonant capacitor, C3, as shown in Figure 4, is:

$K_b = 2$ , center tapped winding.

$K_b = 1$ , single winding.

$$V_{c(pk)} = \frac{\pi (K_a V_{in} K_b)}{2}$$

, [volts] [ 17 ]

12. The primary rms voltage,  $V_{p(rms)}$ , is:

$K_b = 2$ , center tapped winding.

$K_b = 1$ , single winding.

$$V_{p(rms)} = \frac{0.707 \left(V_{c(pk)}\right)}{K_b}, \text{ [volts] [18]}$$

13. The primary maximum reflected secondary current,  $I_{ps}$ , is:

$$I_{ps} = \frac{P_{ot(\text{max})}}{V_{p(rms)}\eta}, \quad [\text{amps}] [19]$$

14. The secondary reflected loads to the primary,  $R_{SR}$ , is:

$K_b = 2$ , center tapped winding.

$K_b = 1$ , single winding.

$$R_{SR} = \frac{V_{p(rms)} (K_b)^2}{I_{ps}}, \text{ [ohms][20]}$$

Note: How the capacitance reactance affects the total percentage of harmonic distortion when:

$$\omega R_{\rm SP}C = 1, \approx [12\%]$$

$$\omega R_{cp}C = 2, \approx [6\%]$$

$$\omega R_{SR}C = 3, \approx [4\%]$$

As a general rule:

$$C_x = \frac{2}{2\pi f(R_{SP})}$$

, [farads]

**15.**  $Q_T$ , is a variable that provides the engineer a little latitude with the capacitor value,  $(1 \le Q_T \le 3)$ .

$$C_x = \frac{Q_T}{2\pi f(R_{SR})}, \quad \text{[farads] [21]}$$

**16.** The reactance,  $X_{cx}$ , of capacitor,  $C_x$ , is: Use a standard capacitor.

$$X_{cx} = \frac{1}{2\pi f C_{r}}$$

, [ohms] [22]

17. The capacitor rms current,  $I_{cx(rms)}$ , is:

$$I_{cx(rms)} = \frac{(0.707)(V_{c(pk)})}{X_{cre}}, \text{ [amps] [23]}$$

**18.** The total primary current,  $I_{tp(rms)}$ , is:

$$I_{pt(rms)} = \sqrt{\left(\left(I_{p(rms)}\right)^2 + \left(I_{cx(rms)}\right)^2\right)}$$

[amps] [24]

**19.** The primary tank inductance,  $L_x$ , is:

$$L_x = \frac{1}{(2\pi f)^2 C_x}$$

, [henrys] [25]

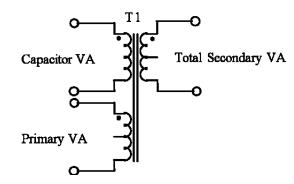

**20.** The total transformer T1 apparent power, P<sub>t</sub>, is:

$$P_{t} = (\text{Prim VA}) + (\text{Sec VA}) + (\text{Cap VA}), \text{ [watts]}$$

$$P_{t} = \left(\frac{P_{ot(\text{max})}(U)}{\eta}\right) + (P_{sa\Sigma}) + \left(K_{b}V_{p(rms)}I_{cx}\right), \text{ [watts]}$$

[26]

Fig. 11. Total Transformer Apparent Power VA.

**21.** The core geometry,  $K_g$ , is:

$K_f$  is the waveform factor = 4.44

$B_{ac}$  is the operating flux density and its value is an engineering judgment based on the frequency and core material.

$$K_{g} = \left(\frac{P_{t}}{0.000029 \left(K_{f}\right)^{2} \left(f\right)^{2} \left(B_{ac}\right)^{2} \alpha}\right), \quad [\text{cm}^{5}] [27]$$

$$K_{g} = \left(\frac{W_{a} A_{c}^{2} K_{u}}{\text{MLT}}\right), \quad [\text{cm}^{5}] [28]$$

#### **Symbols**

- 1.  $A_c$ , core iron area in, cm<sup>2</sup>

- 2.  $\alpha$ , regulation in, percent %

- 3.  $B_{ac}$ , ac flux in, tesla

- 4.  $C_x$ , performance capacitor in, farads

- 5. f, frequency in, hertz

- 6. I<sub>cx</sub>, capacitor current in, amps

- 7. I<sub>o</sub>, output current in, amps

- 8. I<sub>ps</sub>, reflected secondary current in, amps

- 9. I<sub>pt</sub>, primary current in, amps

- 10. J, current density in, amps per cm<sup>2</sup>

- 11. K<sub>a</sub>, conversion factor

- 12. K<sub>e</sub>, electrical operating conditions factor

- 13.  $K_f$ , waveform factor = 4.44 sine and 4.0 square

- 14. K<sub>g</sub>, core geometry in, cm<sup>5</sup>

- 15. K<sub>u</sub>, window utilization factor

- 16. K<sub>b</sub>, winding correction factor, (see text step 11)

- 16. L, inductance in, henrys

- 17. L1, series inductor in, henrys

- 18. l<sub>g</sub>, gap in, cm

- 19.  $L_x$ , primary tank inductance in, henrys

- 20. MLT, Mean Length turn in, cm

- 21.  $\eta$ , efficiency in, percent

- 22. P<sub>o</sub>, output power in, watts

- 23. Pot, total output power in, watts

- 24. P<sub>s</sub>, secondary power in, watts

- 25. P<sub>sa</sub>, secondary apparent power in, watts

- 26.  $P_{\Sigma}$ , total secondary loss in, watts

- 27. P<sub>t</sub>, apparent power in, watts

- 28. R, resistance in, ohms

- 29. R<sub>SR</sub>, reflected secondary resistance in, ohms

- 30. T, total period in, usec

- 31. t<sub>d</sub>, dead time in, usec

- 32. t<sub>on</sub>, transistor on time in, usec

- 33. U, multiplication factor (see text step 4)

- 34. V<sub>c</sub>, resonant capacitor voltage in, volts

- 35. V<sub>d</sub>, diode voltage drop in, volts

- 36. V<sub>in</sub>, input voltage in, volts

- 37. V<sub>o</sub>, output voltage in, volts

- 38. V<sub>p</sub>, primary voltage in, volts

- 39. V<sub>s</sub>, transformer secondary voltage in, volts

- 40. VA, volt-amps in, watts

- 41. W<sub>a</sub>, window area in, cm<sup>2</sup>

- 42. X<sub>cx</sub>, capacitor reactance in, ohms

## Acknowledgment

The author would like to thank Dr. V. Vorperian, Senior Engineer, Power and Sensor Electronics Group, Jet Propulsion Laboratory (JPL), for his help with the Quiet Converter design equations. I would also like to thank Robert Sanchez of Sandia National Laboratories for letting me present this paper.

### Reference

[1] McLyman, C., "Transformer and Inductor Design Handbook," 3<sup>rd</sup> ed., CRC Press, New York, 2004.